Thông thường, việc kiểm thử bảo mật phần cứng chỉ được thực hiện sau khi thiết kế đã được chế tạo thành vi mạch trên công nghệ ASIC hoặc FPGA, gây tốn kém chi phí và thời gian. Trong bối cảnh các cuộc tấn công kênh kề (Side-Channel Attacks) ngày càng tinh vi, việc phát hiện sớm các điểm rò rỉ thông tin trở nên cấp thiết.

Sáng chế đề xuất một quy trình kỹ thuật có hệ thống, cho phép đánh giá mức độ bảo mật của thiết kế phần cứng mật mã (crypto-hardware) ngay trong giai đoạn thiết kế thông qua phân tích lưu vết công suất tiêu thụ được ước lượng bằng mô phỏng, thay vì đợi đến khi sản xuất chip thực tế.

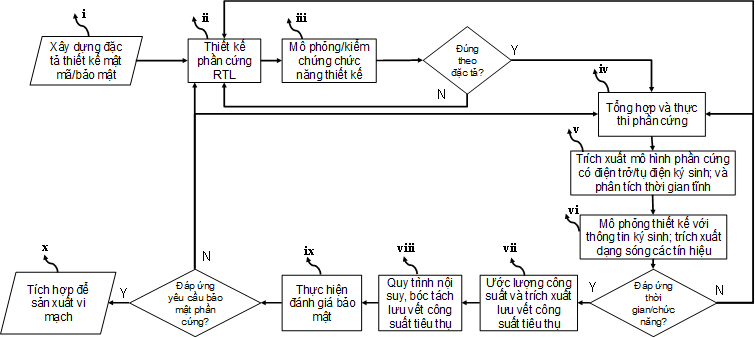

Quy trình được bảo hộ sáng chế bao gồm các bước từ đặc tả thiết kế, mô tả kiến trúc RTL, mô phỏng chức năng, tổng hợp phần cứng, phân tích thời gian và ký sinh, đến ước lượng công suất tiêu thụ và phân tích bảo mật thông qua các kỹ thuật thống kê như T-test, phân tích vi sai (DPA) và phân tích tương quan (CPA). Toàn bộ quy trình được thực hiện trên mô hình thiết kế trước khi gửi đi chế tạo, giúp tiết kiệm đáng kể chi phí và phát hiện sớm các điểm yếu bảo mật có thể bị khai thác.

Sáng chế đặc biệt hữu ích trong việc thiết kế và đánh giá các khối mã hóa phần cứng như AES, RSA, ECC... phục vụ các ứng dụng yêu cầu bảo mật cao như thẻ ngân hàng, căn cước công dân điện tử, hệ thống quân sự, IoT an toàn và thiết bị nhúng bảo mật. Chẳng hạn, các tấn công dựa trên lưu vết công suất tiêu thụ có thể phá giải khóa AES chỉ trong vài phút nếu thiết kế phần cứng không được bảo vệ đúng cách. Giải pháp sáng chế này cung cấp công cụ kỹ thuật mạnh mẽ để kiểm định và nâng cao khả năng chống rò rỉ khóa bí mật trong các thiết kế.

VVH